装置内通信 PSP通信機能 PICマイクロコントローラ応用編より抜粋

16F877にはホストCPUの周辺デバイスとして16F877がインタフェースされることができるスレーブ側のパラレルインタフェースポートを持っています。Z80,6800等の8bit系CPUや8086(V50)等の16bit系CPUのシステムバスに直結することでバスのタイミングにあわせてデータのやりとりをすることができ、PICが周辺I/Oデバイスとなります。

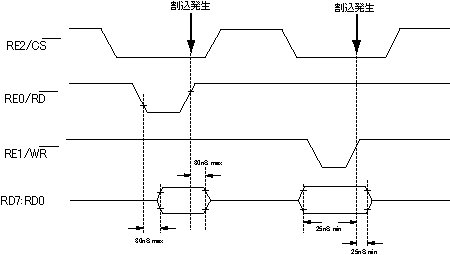

ホストCPUがライト動作を行うと*CSを有効にした後*WRを有効にしてきます。PICは*WRの立ち上がりでデータを受け取ります。*WR信号の立ち上がりで割込が発生しますので、このタイミングでデータを読み取ればよいでしょう。

ホストCPUがリード動作を行うと*CSを有効にした後*RDを有効にしてきます。この時バッファ内のデータがホストCPUに渡されます。*RD信号の立ち上がりで割込が発生しますので、このタイミングにホストCPUがデータを読み取りますから、PICは*CS信号の立ち上がりを確認して終了します。バスインターフェースはこの他にホストに対する割込信号の出力やウェイト信号を取り扱わなければならない場合が考えられ、それら信号をサポートする時は他のポートよりソフト制御で信号を供給します。また、ハードロジックを使用しなければならないケースもあるでしょう。

PSP機能に関する設定はTRISEレジスタにあります。データ線はポートDにあり、制御信号はポートEにあります。このポートはA/Dコンバータとの関係があり、そちらのレジスタセットも必要です。PSP機能を有効にするのはb4のPSPMODEビットをセットします。ホストのライト動作でデータ入力があるとIBFフラグがセットされ、データを読み出すとフラグは自動にリセットされます。もし、データを読取る前に次のデータがホストにより書き込まれた場合IBOVフラグがセットされ以前のデータが消滅してしまったことを示します。PICがデータを出力するとOBFフラグがセットされ、ホストCPUのリード動作で自動にリセットされます。

PICの読み取りが遅いとホストCPUが次のデータを書いてしまいますから前のデータが消滅してしまいます。このような場合はPICのシステムクロックを上げて読み出しを早くするか、BUSY信号を作りホストにアクセスの禁止を示さなければなりません。

バスのスピードは80nS程度のアクセスタイムを持ちますので、高速なインタフェースをとることができますが、データとデータとの間隔はPICの処理スピードに依存します。アクセス時間と処理スピードの違いには設計上の注意が必要です。